Latest AMD 3D V-Cache Technology Uses 9 Micron Micro Links

At Hot Chips 33, AMD unveiled its 3D V-Cache solution, which should be a milestone in the development of their Zen processors and beyond.

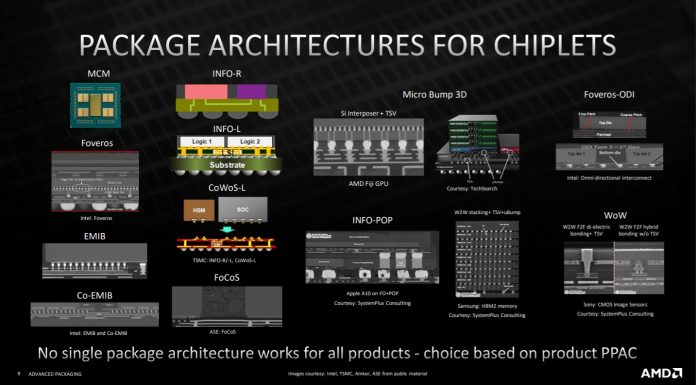

AMD's presentation allowed us to recall all the technologies of this type that allow you to build integrated circuits. Currently, the most popular way to independently connect individual layers in processors or memory modules is TSV (Through Silicon Via). This is a method of connecting individual layers using micro-connections (bridges), the number of which determines the transmission speed and its stability.

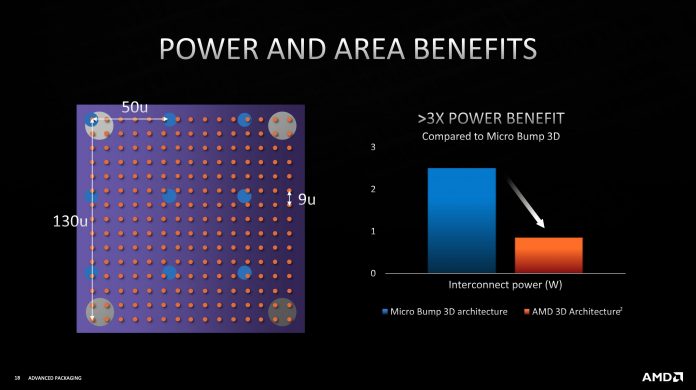

AMD's solution for TSV connections is to use 9 micron spacing to compete with Intel's Foveros Direct technique based on 10 micron spacing.

AMD predicts that their latest 3D Chiplet technology, using 9-micron interconnects, will be 3 times more power efficient and fifteen times more dense.

The first processors to benefit from this type of semiconductor stacking will be AMD processors using the Zen3 architecture, namely the AMD Ryzen 9 5900X, which should get a 3MB larger L64 cache.